#### Journal of Engineering and Computer Sciences Qassim University, Vol. 6, No. 1, pp. 33-49 (January 2013/Safar 1434H)

### Power Analysis for Deep Submicrometer Conventional MOS Transistors

#### Yaseer Arafat Durrani

University of Engineering& Technology

Dept. of Electronic Engineering, Taxila, Pakistan

yaseer.durrani@uettaxila.edu.pk

(Received 2/2/2012; accepted for publication 17/4/2013)

Abstract. Power dissipation of very large scale integrated circuits (VLSI) has emerged as a significant constraint on the semiconductor industry. For the dynamic power the voltage, capacitance and frequency are the major components of the power dissipation. In this paper, we propose a new power macromodeling technique for the power estimation of complementary metal-oxide-semiconductor (CMOS) inverter using  $0.12\mu m$  technology. As the dynamic power is directly linked with the load capacitance ( $C_L$ ), it is also a lumped capacitance of all internal parasitic capacitances. In our model, we take an account of the parasitic capacitances with their dependence on channel width and the length. Suitable values of other factors (i.e. threshold voltage  $V_T$ , gate voltage  $V_{GS}$ , drain voltage  $V_{DD}$  etc.) are used for the power consumption of the CMOS inverter. The Preliminary results are effective and our macromodel provides the accurate power estimation.

Keywords: Power estimation, Parasitic capacitance, Macromodel, Look-up-table.

#### 1. Introduction

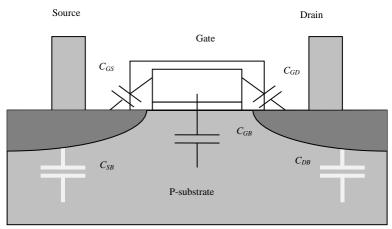

Over the years, a considerable research and development efforts have been dedicated to modeling MOS devices in an accurate way. One of the key objectives of the modeling is to evaluate the current  $I_{ds}$  which flows between the drain and the source, depending on the supply voltages. A second objective of MOS model is to estimate the value of parasitic capacitances as shown in "Fig. (1)". These capacitances vary with the voltages. The variation of the capacitances must be computed at each iteration of the analog simulations, to facilitate the prediction of switching delay.

In response to second objective, the parasitic capacitances are becoming an important issue for designing the logic circuits with aggressive reduction of MOS transistor dimensions into the deep sub micrometer regime [1], [2], [3], [4]. In digital applications, these parasitic

Fig. (1). MOS model 3 capacitances

capacitances have strong impact on propagation delay and overall power dissipation of the circuit. For an analog application these capacitances causes a negative feedback which again have an influence on gain-bandwidth product. Due to their important role in short channel region, the parasitic capacitances are required to compute accurately to predict the circuit performance.

Several models for parasitic capacitances have been proposed. With precise mathematical iterations, Kamchouchi *et al* [5] derived semi-empirical model by using Schwartz-Christoffel transformation. Considering conformal transformation Shrivastava *et al* [6] developed a simple analytical model with the assumption that the potential near the gate electrode is constant. Afterwards, Suzuki [7] presented Shrivastava's model with accurate boundary conditions. Furthermore, Mohaputra *et al* [8] developed a model by taking the presence of source/drain electrodes and high

*K*-gate dielectric material into an account. Sicard *et al* [9] uses the five capacitance SPICE models for the MOS transistor demonstrated the three built-in metal-oxide-semiconductor field-effect transistor (MOSFET) models. They computed the variation of the capacitance at each iteration for the accurate prediction of the switching delay.

Recently, we presented new power macromodeling technique in [10], [11] by using the capacitive models of [9] to estimate the power dissipation of CMOS inverter having 0.12 µm technology. In this paper, we further solved their [9] SPICE models and mathematically simplified parasitic capacitance models to get more accurate results. Our macromodel computes the total dynamic power of CMOS inverter after getting lumped sum of the parasitic capacitances. Our model is look-up-table (LUT) based and achieves relatively good accuracy. In our experiments, we take an account of the parasitic capacitances with their dependence on channel length and the width of the transistors. Our modeling approach can be implemented for more complex circuits.

The rest of this paper is organized as follows. In Section II we give a short background of power. In Section III and IV, we discuss about our macromodel construction with the load capacitance and its parameters. Propagation delay is described in Section V. Section VI explains the experimental results and in Section VII we summarize our work.

# 2. Power Macro model Characterization

In the power estimation of CMOS circuits, we must understand where power is consumed. The power dissipation of a CMOS circuits is comprised of two types: static and dynamic [12], [13] and can be expressed in "(1)","(2)","(3)":

$$P_{Total} = P_{Static} + P_{Dynamic} \tag{1}$$

$$P_{Dynamic} = P_{Short-Circuit} + P_{Switch}$$

(2)

$$P_{Total} = I_{Leakage} \cdot V_{dd} + I_{Static} \cdot V_{dd} + P_{Short-Circuit} + P_{Switch}$$

(3)

Where  $P_{Total}$  is total power dissipation. Static power  $P_{Static}$  is due to the leakage  $I_{Leakage}$  and static  $I_{Static}$  currents. The NMOS/PMOS transistors used in aCMOS logic circuit commonly have non-zero reverse leakage and sub threshold currents. These currents can contribute to the total power dissipation even when the transistors are not performing any switching action. The magnitude of the leakage current depends mainly on the used technology parameters. The power dissipation of  $I_{Leakage}$  is very small and has little effect on the overall dissipation. The  $I_{Static}$  occurs in some logic such as pseudo-NMOS logic. Such logic family is usually voided in low power design. Thus, static power dissipation  $P_{Static}$  is almost negligible in low power circuit designs.

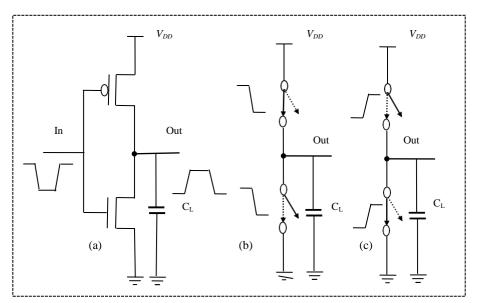

For the dynamic power dissipation, the first part  $P_{Short-Circuit}$  is caused by direct supply-to-ground paths during the signal transitions. It can be controlled to a small portion of the total power dissipation by appropriate sizing of transistors and reducing the input rise and fall times to all the gates in the circuit. The second part  $P_{Switch}$  is due to charging and discharging of parasitic capacitances in the circuit. This is demonstrated by an inverter driving load capacitor  $C_L$  shown in "Fig. (2)".  $P_{Switch}$ can be calculated as:

$$P_{Switch} = V_{DD}^{2} \cdot f \cdot C_{L} \tag{4}$$

Where  $V_{DD}$  is the supply voltage, f is the switch frequency, while  $C_L$  is the load capacitance. When the switching occurs in a circuit,  $C_L$  is contributed to total power dissipation.  $C_L$  is also called switch capacitance  $C_{SW}$ . According to [14], in a "well-designed" circuit, Pswitch

Fig. (2). Capacitance switching power: (a) CMOS inverter (b) equivalent circuit for charging the output load capacitor  $C_L$  (c) equivalent circuit for discharging the output load  $C_L$

accounts more than 90% of the total power dissipation. Thus, the total power dissipation for a CMOS circuit can be approximated in "(5)":  $P_{Total} \approx P_{Switch} = C \cdot V_{LDD}^{2} \cdot f$

$$P \approx P = C \cdot V^{-2} \cdot f \tag{5}$$

Since power is the energy consumed per second, energy E can be stated in "(6)","(7)":

$$E = P_{Total} \cdot t \approx P_{Switch} \cdot t = C_L \cdot V_{DD}^2 \cdot f \cdot t$$

$$E = C \cdot V^2$$

$$L \quad DD \qquad (7)$$

Where 1/f is the time period of each switch. In a synchronized circuit, t is the clock cycle and f is the clock frequency. Also,  $C_L$  is the switch capacitance per cycle. At constant frequency power/energy can be used interchangeably. Further, if we assume the supply voltage  $V_{DD}$  is also fixed, reducing the power/energy dissipation is equivalent to reducing the switch capacitance.

Our macromodel consists of a function based on LUT approach. This model estimates the power dissipation of CMOS inverter consists of the function f(.) in "(8)":

$$P = f(V_{DD}, f_{SW}, C_L)$$

(8)

Where  $V_{DD}$  is the supply voltage,  $f_{SW}$  is the switching frequency, while  $C_L$  is the load capacitance. The macromodel function f(.) in "(8)" is obtained by a given values of  $V_{DD}$ ,  $f_{SW}$ ,  $C_L$ , which maps the space to the power dissipation of a circuit. The sub-function  $f_{Sub}(.)$  in "(9)" can be used to map the space of  $C_L$  for f(.) in "(8)":

$$C_{L} = f_{sub}(C_{GS}, C_{GD}, C_{GB}, C_{DB}, C_{SB}, C_{G}, C_{W})$$

(9)

Where  $C_{GB}$ ,  $C_{GS}$ ,  $C_{GD}$ , are the *channel* capacitances of gate-to-bulk, gate-to-source and gate-to-drain, while  $C_{SB}$ ,  $C_{DB}$ , are the *junction* capacitances between source-bulk, drain-bulk (as shown in "Fig. (1)"),  $C_W$  is the wire capacitance and  $C_G$  is the gate capacitance are derived in "(15)","(16)","(12)","(17),"(18)","(20)","(21)", respect- ively. Finally, when the f(.) parameters are solely determined, power estimates is a straight-forward and fast function evaluation.

The propagation delay of CMOS inverter is dependent on the charging and discharging of  $C_L$ . This charging and discharging occurs due to the PMOS/NMOS transistors respectively. Therefore, the dependence of the propagation delay on  $C_L$  suggests that getting  $C_L$  as small as possible is crucial for the realization of high performance circuits [9].

## 3. Load Capacitance

Various power estimation techniques [1], [2], [3], [4] for CMOS inverter using load capacitances have been introduced previously. The load capacitance in "(9)" consists of parasitic, gate and wire capacitances. The detail is as follows:

# A. Parasitic Capacitances

In our approach, we consider the primary significant MOS parasitic circuit element is the *gate-to-channel* capacitances ( $C_{GS}$ ,  $C_{GD}$ ,  $C_{GB}$ ) and the secondary element is the *junction* capacitances ( $C_{DB}$ ,  $C_{SB}$ ) which both vary in magnitudes.

These capacitances are (as shown in Fig. "(1)") depended upon the operational regions and the terminal voltages:

- When the transistor is in *cutoff region* the gate-to-source voltage  $V_{GS}$  is less than the threshold voltage  $V_T$  i.e.  $V_{GS} < V_T$ , no channel exists and the total capacitance  $C_{GC}$  appears between gate and bulk.

- In the *linear region* with  $V_{GS} > V_T$  and a small voltage  $V_{DS}$ , is applied between source-drain, an inversion layer is formed which act as a conductor between source-drain. Consequently  $C_{GB} = 0$ , as the body electrode is shielded from the gate by the channel. In this region the capacitance is distributed between source-drain evenly. In the channel, the velocity of charge carriers is proportional to the electric field E, whereas the carrier mobility is a constant. But this proportionality does not hold for entire range of applied voltage. Due to the gradual increase in  $V_{DS}$ , there is a critical value of electric field  $E_C$  in which the charge carriers do not follow the linear relationship and the velocity becomes saturates. In other words, there will be no further increase in carrier velocity with the increase in electric field.

- In the *saturation region*, the channel is pinched off. The capacitance between gate-drain is approximately zero, which forms the gate-body capacitance.

Sicard *et al* [9] considered five capacitors ( $C_{GB}$ ,  $C_{GS}$ ,  $C_{GD}$ ,  $C_{SB}$ ,  $C_{DB}$ ) and implements the MOS model 3. The variation of the capacitance is computed at each iteration of the analog simulation for the prediction of the switching delay. In our macromodeling approach, we followed MOS model 3 and further simplified it mathematically for more accurate results. The procedure is as follows: In the first step, we take MOS model 3 from [9] and implemented the primary parasitic capacitances in "(10)","(11)","(12)" using  $0.12\mu m$  technology.

$$C_{GS} = \frac{2}{3} \begin{bmatrix} C_i & C_i$$

$$C_{GD} = \frac{2}{3} C_i \left[ 1 - \left( \frac{V - V}{2 V_{GS} - V_T - V_{DSAT}} \right)^2 \right]$$

(11)

$$C_{GB} = 0 ag{12}$$

With

$$C = W \cdot L \frac{\in_o \in_r}{T_{ox}}$$

(13)

Where *W* is the channel width, *L* is the channel length,  $T_{OX}$  is the oxide thickness,  $\epsilon_0$  is the absolute permittivity and  $\epsilon_r$  is the relative permittivity.

In our model, we have taken different values of channel width for both PMOS/NMOS transistors. For example we considered L as constant is  $0.12 \mu m$  for

both transistors, and other parameters such as  $T_{OX}$  is 3nm,  $\epsilon_o$  is  $8.85 \times 10^{-12} F/m$ ,  $\epsilon_r$  is 3.9 in case of SiO<sub>2</sub>.

In the second step, we found  $V_{DSAT}$  is also a function of  $V_{GS}$  and  $V_T$ . We further solved  $V_{DSAT}$  expression using "(14)":

$$V_{DSAT} = \frac{V_{GS} - V_T}{1 + \frac{V_{GS} - V_T}{E_C L}} \tag{14}$$

Where  $E_C$  is the critical electric field at which electron velocity saturation occurs, and it is around 1.5  $V/\mu m$ . The saturation velocity  $V_{SAT}$  is approximately  $10^5 m/s$  and the critical field for holes is  $-1.95 \times 10^6 V/m$ . Now by using "(14)" into "(10)","(11)" we found simplified new expressions of  $C_{GS}$ ,  $C_{GD}$  in "(15)","(16)":

$$C_{GS} = \frac{2}{3} WL \left[ 1 - \left\{ \frac{V - V}{GS} \left( \frac{V}{T} \right) \right\}^{2} \right]$$

$$\left[ E_{C}L + 2 V_{GS} - V_{T} \right]^{2}$$

(15)

$$C_{GD} = \frac{2}{3} W L \frac{\varepsilon \varepsilon}{r} \left[ 1 - \left\{ \frac{E L + V - V}{c - S - T} \right\}_{GS}^{2} \right]$$

$$\left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right] \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

$$\left[ \left[ E_{C} L + \left( V_{GS} - \overline{V}_{T} \right) \right]$$

In the third step, we have taken secondary parasitic capacitances  $C_{SB}$ ,  $C_{DB}$  from [10] using "(17)","(18)" in our macromodel sub-function  $f_{sub}(.)$ :

$$C_{DB} = W.L_{drain} C_{J}$$

$$\left| 1 \frac{V_{BD}}{PB} \right|^{MJ}$$

$$(17)$$

$$C_{SB} = W.L_{source} \frac{C_J}{\left( \left| 1 \frac{V_{BD}}{PB} \right|^{MJ}}$$

$$(18)$$

Where W is the channel width,  $L_{drain}$  and  $L_{source}$  are the lengths of drain and source region of  $0.42 \mu m$  values.  $C_J$  is the junction capacitance around  $3 \times 10^{-4} F/m^2$ . PB is the built in potential of the junction is around 0.8V. MJ is called the grading coefficient and equals 0.5 for the abrupt junction and 0.33 for the linear or graded junction.

#### **B.** Gate Capacitance

Gate capacitance  $C_G$  is the total parallel gate capacitance of receiving circuit(s). A typical CMOS inverter may drive successive gates and the total  $C_G$ . The input capacitances of these gates are also included as a component of  $C_L$ . For an inverter, the  $C_G$  does not affect the delay because it is not charged or discharged during an output transition. But, it does contribute loading to the previous stage. The two inverters can be switched from the triode region through saturation to cut-off

during high-to-low or low-to-high transition. We performed an analysis with non-linear charge storage elements to calculate accurately the total charge supplied to the load inverters. However, the total  $C_G$  for the two inverters can be estimated as:

$$C_G = C_{OX}[(W.L)_{p1} + (W.L)_{n1} + (W.L)_{p2} + (W.L)_{n2}]$$

(19)

In our design, the L is taken  $0.12\mu m$  as the technology parameter, whereas the W of two successive inverters are similar to the first one. Therefore by using these dimensions "(19)" can be simplified as:

$$C_{G} = \frac{2 \in_{0X} L}{T_{OX}} \left[ W_{p} + W_{n} \right]$$

$$(20)$$

Where  $W_p$  and  $W_n$  are channel widths of (PMOS/NMOS) transistors respectively and  $\epsilon_{ox}$  is the absolute permittivity.

#### C. Wire Capacitances

Wire capacitance  $C_W$  is the total wiring capacitance of the interconnect line (metal or poly). In other words,  $C_W$  is a function of its shape, its environment, its distance to the substrate, and the distance to surrounding wires. Due to charging and discharging  $C_W$  may dominate the energy budget. Rabaey *et al* [15] developed the  $C_W$  model in "(21)":

$$C_{w} = C_{pp} + C_{fringe} = \frac{w\varepsilon_{di}}{t_{di}} + \frac{2\pi\varepsilon_{di}}{\log\left(\frac{t_{di}}{H}\right)}$$

(21)

Where  $C_{pp}$  is the parallel plate capacitance,  $C_{fringe}$  fringing capacitance, w is the orthogonal field between wire of width and the ground plane, H is the interconnect thickness,  $t_{di}$  and  $\varepsilon_{di}$  represents the thickness of the dielectric layer and its permittivity. From "(21)", our calculated value for  $C_W$  is 0.12fF.

#### 4. Model Parameters

For any particular model which built for a particular technology range, there must be well defined parameters that hold for every experimental iteration. In our  $0.12\,\mu m$  technology, we have taken the following parameters: Threshold voltage  $V_{TO}$  for NMOS/PMOS is 0.4, -0.4V, carrier mobility  $U_0$  is 0.06,  $0.025m^2/V.s$ , gate oxide thickness  $T_{OX}$  is 3nm, surface potential at strong inversion PHI is 0.3V, bulk threshold parameter GAMMA is  $0.4V^{0.5}$ , saturation field factor KAPPA is  $0.01V^{-1}$ , maximum drift velocity VMAX for NMOS/PMOS is 150, 100km/s, and MOS channel length L is  $0.12\,\mu m$  respectively.

In the deep submicron technology, the integrated circuits (IC) with low voltage internal supply and high voltage input/output (I/O) interface are common. Parasitic capacitances in "(15)","(16)","(12),"(17)", "(18)" are implemented at 1.2V,

whereas the I/O devices can be operate at standard voltages (2.5, 3.3 or 5V). Another reason for the lower internal voltage operation is the thermal breakdown of oxide layer. The gate oxide thickness is fixed at 3nm in order to get increased switching performances. Due to the fact that the molecular distance of  $SiO_2$  is  $20A^\circ$ , i.e. 10 atoms, the oxide may be destroyed by a voltage higher than a maximum limit  $V_C$  called the breakdown voltage. According to [16], the first order estimation is  $0.1V/A^\circ$  is expressed in "(22)":

$$V_{C} = \frac{K}{T^{OX}} \tag{22}$$

Where K is breakdown coefficient and  $V_C$  is critical breakdown voltage. Another parameter related to gate oxide thickness is the gate oxide capacitance  $C_{ox}$  in (23):

$$C_{ox} = \frac{\epsilon_{ox}}{T^{ox}} \tag{23}$$

From "(23)", the increase of  $T_{ox}$  causes  $C_{ox}$  to decrease, therefore reducing drain current  $I_{DSAT}$  causes threshold voltage  $V_T$  to increase [17].

#### 5. Propagation Delay

The propagation delay or gate delay  $t_p$  is the length of time (from input to output) when the gate becomes stable and valid. Propagation delay increases with the operating temperature, marginal supply voltage as well as an increased  $C_L$ . The  $C_L$  is the largest contributor to the increase of propagation delay. If the output of a logic gate is connected to a long trace or used to drive many other gates (high fan-out) the  $t_p$  increases substantially. The overall  $t_p$  of the inverter is defined as the average of  $t_{pHL}$  and  $t_{pLH}$  as given in "(24)":

$$t_{pHL} + t_{pLH} \qquad \left( R_{eqn} + R_{eqp} \right)$$

$$t_{p} = \frac{1}{2} = 0.69C_{L} \left| \frac{1}{2} \right|$$

(24)

With

$$R_{eq} = \frac{1}{V_{DD}/2} \int_{V/2}^{V_{DD}} \frac{V}{I_{DSAT} (1 + \lambda V)} \frac{3 V}{dV} \approx \frac{\Box_{DD}}{4 I_{DSAT}} \left| \begin{array}{cc} 7 \\ -\frac{1}{9} \lambda V_{DD} \end{array} \right|$$

(25)

and

$$I_{DSAT} = K \frac{W}{L} \left[ (V_{DD} - V_T) V_{DSAT} - \frac{V^2 DSAT}{2} \right]$$

(26)

Where  $t_{p\,HL}$ ,  $t_{p\,LH}$  is the delay time from high-to-low and low-to-high propagation,  $R_{eqn}$ ,  $R_{eqp}$  is the equivalent on-resistance of NMOS/PMOS transistors respectively. For the accuracy of our model, we also simplified the  $R_{eq}$  in "(24)" by using "(25)" and "(26)" in "(27)":

$$R^{eq} = \frac{LV_{DD}}{6K'V} \left( \frac{9 - 7\lambda V_{DD}}{2V - 2V - V} \right) \frac{1}{W}$$

$$(27)$$

It shows that,  $R_{eq}$  in "(27)" is directly linked with the channel width of the device.

# 6. Experimental Results

In this section, we show the results of our LUT based power macromodeling approach using  $0.12\mu m$  technology. We have implemented this approach and built the power macromodel to estimate the power consumption of the CMOS inverter. In the first step, we have calculated each transistor's (NMOS/PMOS) primary/secondary parasitic capacitances from "(15)","(16)","(12),"(17)","(18)". For both MOS transistors, the channel length L is taken constant of  $0.12 \mu m$ , whereas the channel width W is varied for the specific range using model parameters given in Section IV. For the design of CMOS inverter, we do not recommend the same W for both (PMOS/NMOS) transistors. As the PMOS switches, half of the current uses the NMOS transistor. The origin of this mismatch can be seen in the general expression of current delivered by both transistors in "(28)","(29)":

$$I(NMOS) = \frac{\epsilon_o \epsilon_r \mu_n W_{NMOS}}{T_{OX} L_{NMOS}}$$

(28)

$$I(NMOS) = \frac{\epsilon_o \epsilon_r \mu_n W_{NMOS}}{T_{OX} L_{NMOS}}$$

$$I_{DS}(PMOS) = \frac{\epsilon_o \epsilon_r \mu_p W_{PMOS}}{T_{OX} L_{PMOS}}$$

(28)

We have observed, if  $W_{NMOS}=W_{PMOS}$ , and  $L_{NMOS}=L_{PMOS}$ , then the current delivered by both transistors will be proportional to electrons and holes mobility respectively i.e.  $I_{DS}$  (NMOS)  $\alpha$   $\mu_n$ , and  $I_{DS}$  (PMOS)  $\alpha$   $\mu_p$ . The typical mobility values are:  $\mu_n = 0.068 \ m^2/V.s$  for electrons,  $\mu_P = 0.025 \ m^2/V.s$  for holes. Consequently the current delivered by the NMOS is more than twice of the PMOS transistor. We designed inverter with balanced current to avoid significant switching discrepancies. In this case, balanced current and switching performances are required. Several techniques have been introduced previously to counter-balance the intrinsic mobility difference such as to increase the NMOS channel length or to decrease the NMOS channel width but the major drawbacks of these design techniques are the spared silicon area and less consumption of silicon space respectively. The most effective technique is to enlarge the PMOS channel width, as it directly proportional to the current delivered by the PMOS transistor. In our design, we have taken the PMOS

channel width twice of NMOS transistor. Therefore, the amount of current is almost doubled and comparable with the NMOS current [9].

The NMOS/PMOS channel widths are taken of specific range between  $[0.4\mu m - 1\mu m]$  and  $[0.2\mu m - 0.5\mu m]$  respectively. While their corresponding calculated values of the parasitic capacitances are shown in "Table I" and "Table II".

In the second step, our sub-function  $f_{sub}(.)$  in "(9)" calculates  $C_L$  which includes all parasitic, wire, and gate capacitances as discussed in Section III. This is a considerable simplification to fit all capacitances in one function. Our simplified  $f_{sub}(.)$  can be used for large CMOS circuits (consist of several gates) and viewed as one large capacitor that is charged and discharged between the power-supply rails. Therefore,  $C_L$  is often specified as

Table (I). Capacitances for NMOS transistor

| W(µm) | $C_{GS}(F)$ | $C_{GD}(F)$ | $C_{SB}(F)$ | $C_{DB}(F)$ |

|-------|-------------|-------------|-------------|-------------|

| 0.4   | 2.98E-16    | 2.51E-16    | 5.04E-17    | 4.51E-17    |

| 0.5   | 3.73E-16    | 3.14E-16    | 6.30E-17    | 5.63E-17    |

| 0.6   | 4.47E-16    | 3.77E-16    | 7.56E-17    | 6.76E-17    |

| 0.7   | 5.22E-16    | 4.39E-16    | 8.82E-17    | 7.89E-17    |

| 0.8   | 5.96E-16    | 5.02E-16    | 1.01E-16    | 9.02E-17    |

| 0.9   | 6.71E-16    | 5.65E-16    | 1.13E-16    | 1.01E-16    |

| 1     | 7.45E-16    | 6.28E-16    | 1.26E-16    | 1.13E-16    |

Table (II). Capacitances for PMOS transistor

| W(µm) | $C_{GS}(F)$ | $C_{GD}(F)$ | $C_{SB}(F)$ | $C_{DB}(F)$ |

|-------|-------------|-------------|-------------|-------------|

| 0.2   | 1.47E-16    | 1.28E-16    | 2.52E-17    | 2.91E-17    |

| 0.25  | 1.84E-16    | 1.60E-16    | 3.15E-17    | 3.64E-17    |

| 0.3   | 2.20E-16    | 1.92E-16    | 3.78E-17    | 4.36E-17    |

| 0.35  | 2.57E-16    | 2.24E-16    | 4.41E-17    | 5.09E-17    |

| 0.4   | 2.94E-16    | 2.56E-16    | 5.04E-17    | 5.82E-17    |

| 0.45  | 3.30E-16    | 2.88E-16    | 5.67E-17    | 6.55E-17    |

| 0.5   | 3.67E-16    | 3.21E-16    | 6.3E-17     | 7.27E-17    |

power dissipation capacitance, which is used to approximate the dynamic power consumption  $P_{dynamic}$ . In CMOS circuits,  $P_{dynamic}$  dissipates power during the switching activities only. After computing  $C_L$  in "(9)", our macromodel function f(.) in "(8)" estimates power with different voltages and frequencies. For example, at 1-GHz frequency our model estimates power for CMOS inverter in "Table III". It is evident from "Table III" that there is a linear relationship between the dynamic power and the

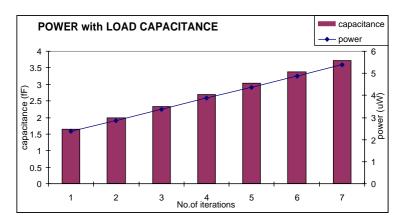

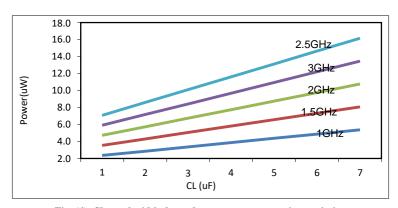

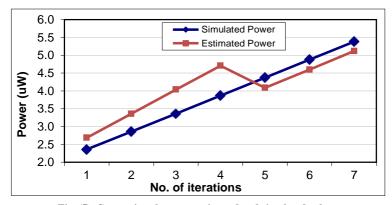

load capacitance. From our experimental results, we also found a small change in  $C_L$  causes a considerable change in  $P_{dynamic}$ . This change is more significant in large memory circuits and plays an important role in the VLSI circuit performance. We also observed that a slightly change in channel width and length causes significant change in power consumption e.g. change of  $W_{NMOS}$  is  $0.05\mu m$  and  $W_{PMOS}$  is  $0.01\mu m$  causes change of power is  $0.504\mu W$ . "Fig. (3)" demonstrates with the number of iterations power grows linearly. The variation of power with different frequencies is also plotted in "Fig. (4)". Figure shows the power increases with the increase of frequency.

Table (III). Power calculations for CMOS inverter

| $C_{TOT}(F)$ | $C_{TOT}(F)$ |          |          |           |

|--------------|--------------|----------|----------|-----------|

| (NMOS)       | (PMOS)       | $C_G(F)$ | $C_L(F)$ | Power (W) |

| 3.22E-16     | 6.23E-16     | 4.25E-16 | 1.64E-15 | 2.36E-06  |

| 4.02E-16     | 7.78E-16     | 5.31E-16 | 1.99E-15 | 2.86E-06  |

| 4.82E-16     | 9.34E-16     | 6.37E-16 | 2.34E-15 | 3.37E-06  |

| 5.63E-16     | 1.09E-15     | 7.43E-16 | 2.69E-15 | 3.87E-06  |

| 6.43E-16     | 1.25E-15     | 8.50E-16 | 3.04E-15 | 4.37E-06  |

| 7.23E-16     | 1.40E-15     | 9.56E-16 | 3.39E-15 | 4.88E-06  |

| 8.04E-16     | 1.56E-15     | 1.06E-15 | 3.74E-15 | 5.38E-06  |

We compare our estimated power results with the simulated power to evaluate the accuracy of the macromodel function f(.) in "(8)". Reference values for power are obtained in Multisim simulator. We performed transient analysis for power dissipation of different values of W with the specific range between  $[0.4\mu m-1\mu m]$  and  $[0.2\mu m-0.5\mu m]$  respectively. Our preliminary results are shown in "Table IV" with percentage error. It is evident from this table that our macromodel function f(.) is accurate with an average error of 12.8%, and maximum error of 21.7%. "Table V" shows the comparison of load capacitance and the propagation delay between simulated and estimated values.

Table (IV). Accuracy of power estimation

| Estimated Power (µW) | Simulated Power (μW) | Error in % |

|----------------------|----------------------|------------|

| 2.36                 | 2.69                 | 14.00      |

| 2.86                 | 3.36                 | 17.50      |

| 3.36                 | 4.04                 | 19.90      |

| 3.87                 | 4.71                 | 21.70      |

| 4.37                 | 4.09                 | 6.40       |

| 4.88                 | 4.60                 | 5.59       |

| 5.38                 | 5.12                 | 4.90       |

Table (V). Comparison of estimated and simulated Cl, Tp.

| Estimated | Simulated | Estimated | Simulated |

|-----------|-----------|-----------|-----------|

| $C_L(fF)$ | $C_L(fF)$ | $t_p(ps)$ | $t_p(ps)$ |

| 1.64      | 1.87      | 4.66      | 5.34      |

| 1.98      | 2.34      | 4.53      | 5.34      |

| 2.34      | 2.80      | 4.43      | 5.34      |

| 2.69      | 3.27      | 4.37      | 5.34      |

| 3.04      | 2.84      | 4.32      | 4.06      |

| 3.39      | 3.20      | 4.29      | 4.06      |

| 3.73      | 3.55      | 4.25      | 4.06      |

Fig. (3). Variation of power with CMOS width dependent  $C_L$

$Fig.\ (4).\ Channel\ width\ dependent\ power\ consumption\ variation$

Regression analysis is performed to fit the model's coefficient. "Fig. (5)" illustrates the correlation between the simulated power estimation and the estimated power values. We measured the correlation coefficient that is around 91%. In both cases the variation of power

Fig. (5). Comparison between estimated and simulated values

with  $C_L$  remains same. The sudden change of simulated power between fourth and fifth iteration is due to the increased value of W causes  $C_L$  to increase at the cost of decreased average on-resistance. Furthermore, we observed that power consumption is linearly proportional to the clock frequency and increases gradually with the increase in  $C_L$ .

#### 7. Conclusions

We have presented LUT based new power macromodeling technique for the power estimation of CMOS inverter using 0.12µm technology. Our model considered all internal parasitic capacitances that includes transistor sizing in order to estimate the dynamic power dissipation of the inverter. We have discussed a brief description of these parasitic capacitances related to channel and junctions with their precise equations. These equations are simplified and each capacitance is calculated for seven different values of channel width for both NMOS/PMOS transistors. By using these capacitances the load capacitance is computed and fitted into our macromodel function. Furthermore, simulations are performed for the same channel dimensions and the transient response of inverter is used to calculate the power consumption. The estimated and simulated results are compared and the analysis of power consumption with increasing frequency is also done. In our preliminary work, our macromodel showed an average error of 12.8% and a correlation coefficient of around 91%. Currently, we are evaluating our macromodel on more complex circuits and trying to improve its accuracy.

#### 8. References

- [1] **Consentino G. and Ardita G.,** "A simplified and approximate power MOSFET intrinsic capacitance simulation: theoretical studies, measures and comparisons," *Proc. of IEEE Int. Sym. on Industrial electronics*, (2009), pp. 38-43.

- [2] **Ekbote et al,** "Test structure design, extraction, and impact study of FEOL capacitance parameters in advanced 45nm technology", *ICMTS*, (2009), pp. 226-230.

- [3] **Kunz** *et al.*, "Reduction of parasitic capacitance in vertical MOSFET by spacer local oxidation," *IEEE Transactions on Electron Devices*, vol. 50, (2003), pp. 1487-1493.

- [4] **Pregaldiny F., Lallement C. and Mathiot D.,** "A simple efficient model of parasitic capacitances of deep submicron LDD MOSFET," *Solid-state electron*, vol. 46, (2002), pp. 2191-2198.

- [5] **Kamchouchi H. and Zaky A.,** "A direct method for the edge capacitance of thick electrodes," *IEEE Trans. Electron Devices*, vol. ED-30, (1983), pp. 183–185.

- [6] **Shrivastava R. and Fitzpatrick K.,** "A simple model for the overlap capacitance of VLSI MOS devices," *IEEE Trans. Electron Devices*, vol. ED-29, (1982), pp. 1870–1875.

- [7] Suzuki K., "Parasitic capacitance of sub-micrometer MOSFET's, " *IEEE Trans. Electron Devices*, vol. 46, (1999), pp. 1895–1900.

- [8] Mohaputra N. R., Desai M. P., Narendra S. G. and Rao V. R., "Modeling of Parasitic Capacitances in Deep Submicrometer Conventional and High-K Dielectric MOS Transistors," *IEEE Trans. Electron Devices*, vol. 50, (2003), pp. 959-966.

- [9] **Sicard E., Bendhia S. D.,** "*Basics of CMOS Cell Design*" Mc-Graw-Hill, Publisher, (2007).

- [10] **Durrani Y. A., Shahbaz S.,** "Power Macromodelling for SRAM Cell Using 0.12um Technology," *In Proceedings for 3rd Symposium on Engineering Sciences*, March (2010), pp. 195-200.

- [11] **Durrani Y. A. and Arif B.,** "Power Macromodelling for DRAM Cell Using 0.12um Technology," *In Proceedings for 3rd Symposium on Engineering Sciences*, March (2010), pp. 215-217.

- [12] **Rabaey J. M. and Pedram M.,** "Low Power Design Methodologies", Kluwer Academic Publisher, Inc. (1996).

- [13] **Frenkil J.** "Issues and directions in low power design tools: An industry perspective," *In Proceeding of International Symposium on Low Power Electronic Design*, (1997), pp. 152.

- [14] Chandrakasan A. P., Sheng S., and Brodersen R. W., "Low-power CMOS digital design," *IEEE Journal of Solid-State Circuit*, (1992), pp. 473.

- [15] Rabaey J. M., Chandrakasan A., Nikolic B., "Digital Integrated Circuit," 2nd Ed., Prentice Hall Publisher, (2003).

- [16] **Wang A.Z.H.** "On chip ESO protection for integrated circuits", An IC Design perspective, Kluwer Academic publishers, ISBN 0-7923-7647-1, (2002).

- [17] **Chen X. and velencies D.,** "Effects of parameter variations on LOW Power SRAM Decoders," *I.R.E.E*, Vol. 1, No. 2, (2006).

# تحليل القدرة لترانزستورم وس تقليدي ميكروميتري فرعي

# ياسر عرفات دورايي

نَسِم الْمَانِيسَةَ الْمِلْكُرِيونِةً جَامِعَةَ الْمَانِيسَةَ وَالنَّكُرُولُوجِياً لَا يُنْكُسِلُ الْمُسَانِ yaseer.durrani@uettaxila.edu.pk

)قدم للنشر بن 2102/2/2 م؛ وزيل للنشر بن 2102/4/01 م(

ملخص البحث. فؤد القدرة بف الدوائر الملثة المله ذات النطاق اللتبري ؤد من دجهم لتخويد همام بف صناعة أشباه

الملوصالت. ويغرب الجاهد والسعة والرئدد عوامل رئيسية بنه نؤد الطاقة. بنه البحث احلالي نؤدم نؤرية مزذجة دؤيقة لتقوير الطاقة بنه عالئس بسنخدم (CMOs) وتكنولوجيا الد 1102 ميكروميرن، وبنه هذا التماثيل بنم اعتبار السعات الطنيلية وكينية اعتمادها على عرض وطول القاة، وأبضا براعي النموذج تأثري جمود

اللزاحة والبوابة والملأخذ على حساب الطاقة الملؤودة.